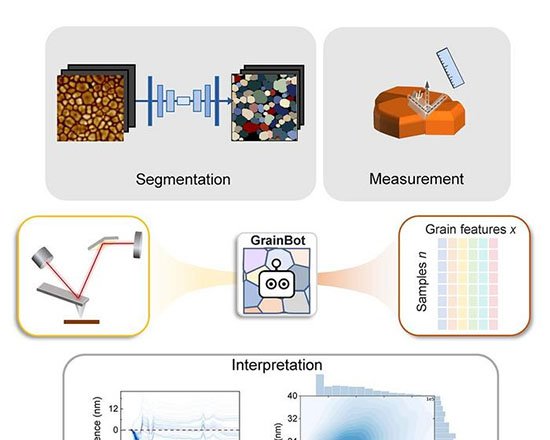

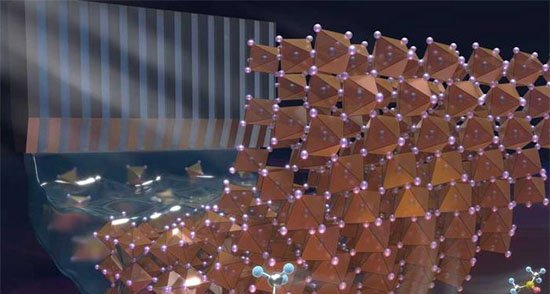

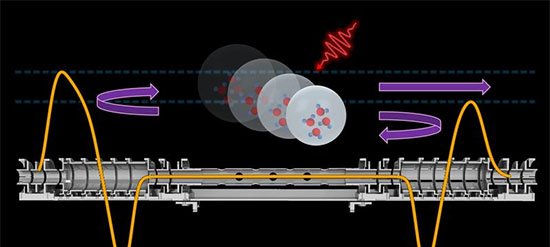

Um grupo da Universidade Nacional de Seul (SNU) apresentou um roteiro detalhado para a engenharia de gate stack em transistores bidimensionais, etapa considerada decisiva para substituir a tecnologia de silício em futuros chips. O estudo, liderado pelo professor Chul-Ho Lee, do Departamento de Engenharia Elétrica e de Computação, foi publicado em 14 de outubro de 2025 na revista Nature Electronics.

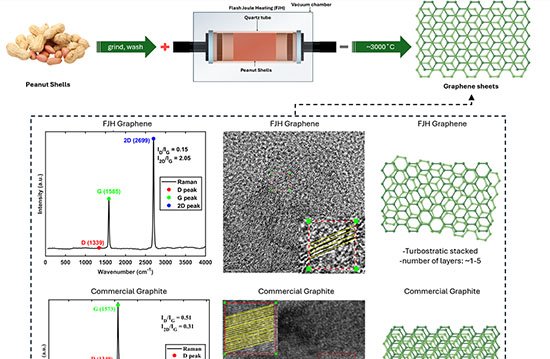

Com a miniaturização dos circuitos de silício próxima a seus limites físicos, semicondutores 2D — materiais com espessura de apenas uma camada atômica — surgem como alternativa para manter desempenho em escalas nanométricas extremas. Grandes fabricantes como Samsung, TSMC, Intel e IMEC já investem na tecnologia, planejando lançamentos a partir da metade da década de 2030.

Desafio do gate stack

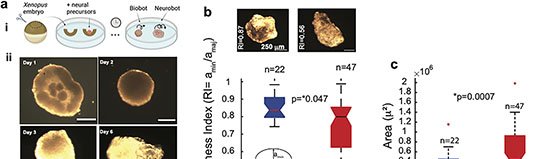

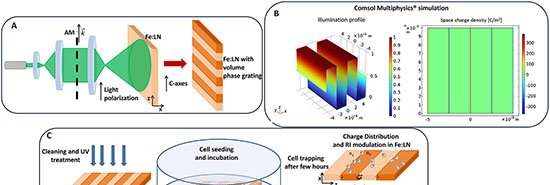

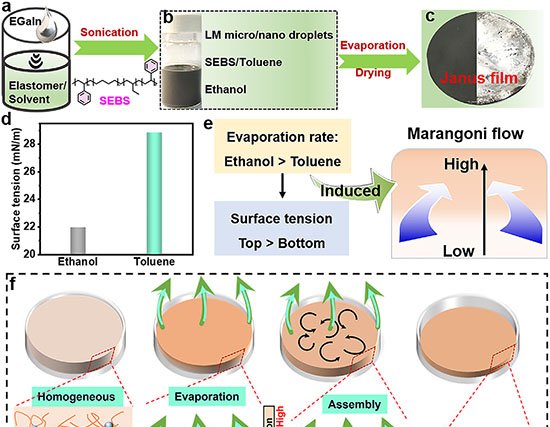

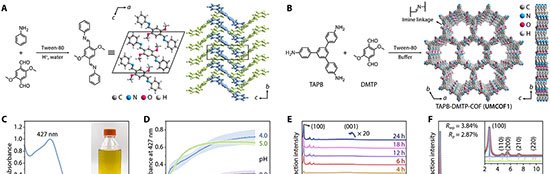

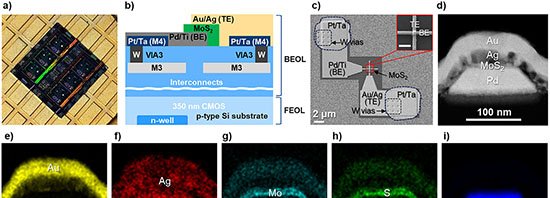

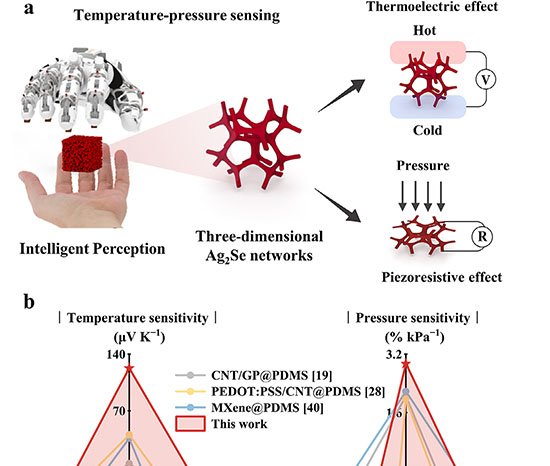

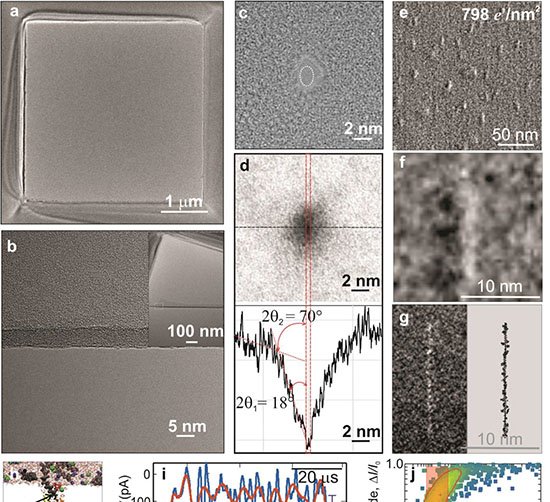

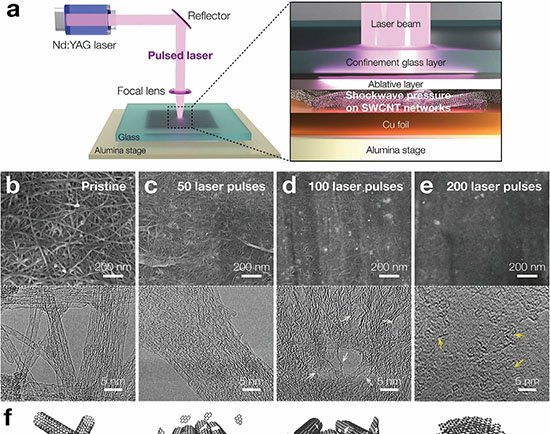

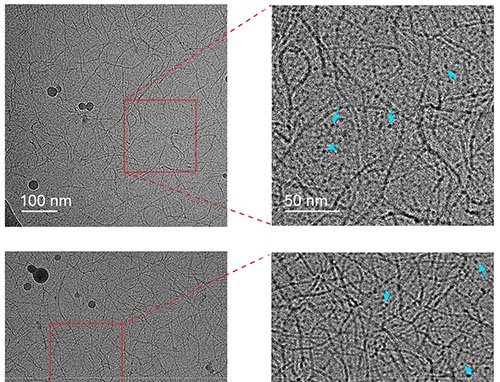

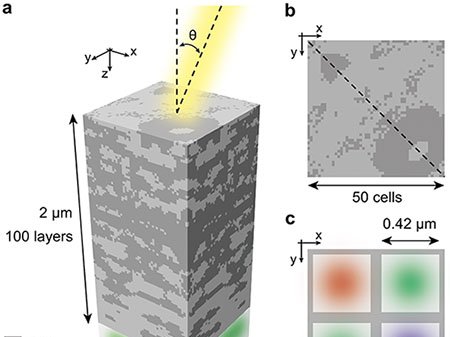

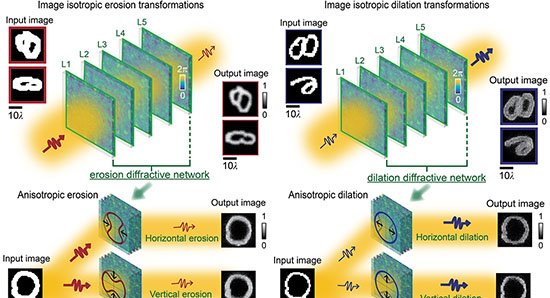

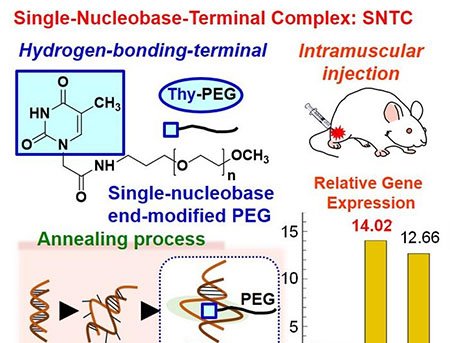

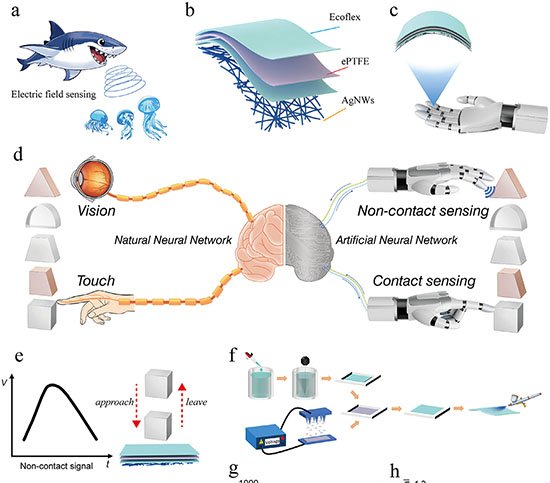

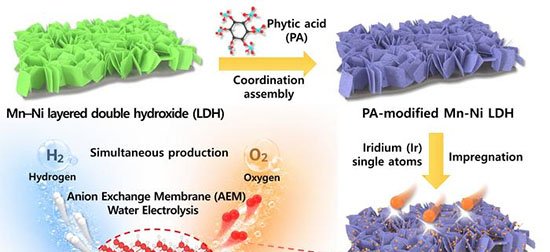

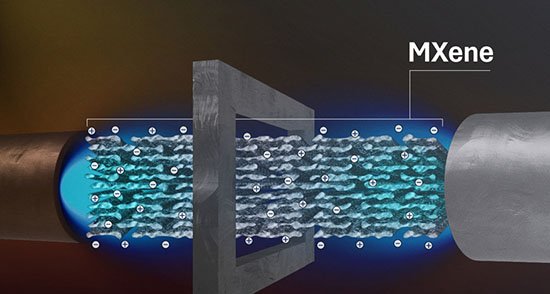

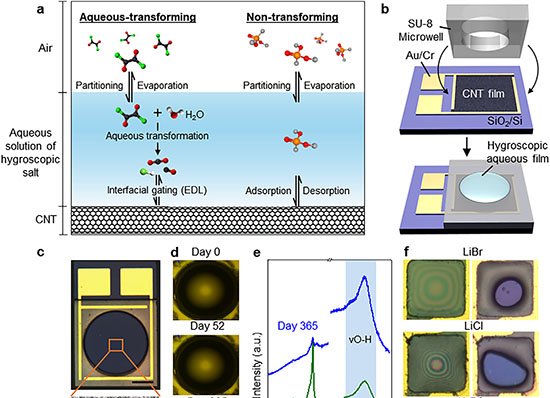

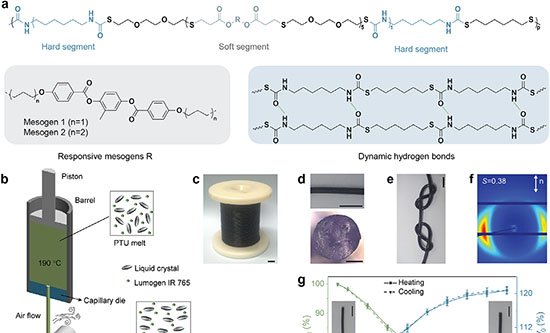

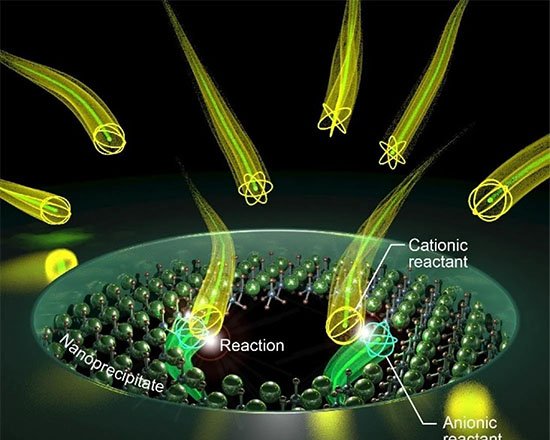

O principal obstáculo para a adoção comercial dos transistores 2D é a integração do gate stack, estrutura responsável por controlar o fluxo de corrente. Processos tradicionais de silício costumam danificar a camada isolante, gerar defeitos e provocar vazamento elétrico, comprometendo o rendimento dos dispositivos.

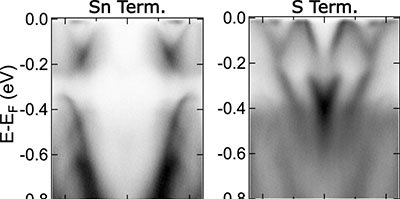

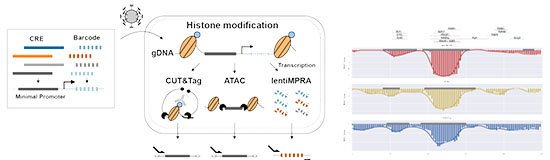

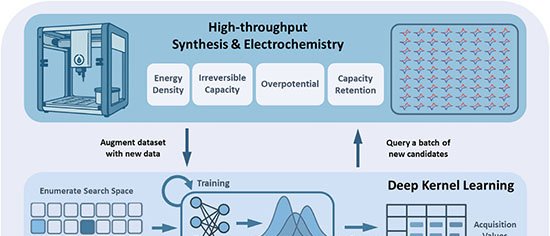

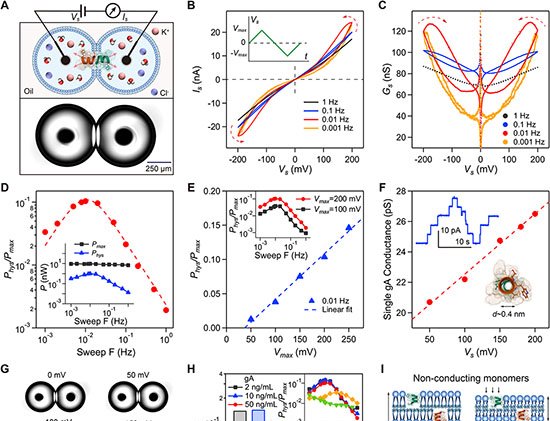

A equipe da SNU avaliou cinco métodos de integração — incluindo variantes com dielétricos de van der Waals — comparando qualidade de interface, espessura de óxido e vazamento de porta. Os resultados foram confrontados com metas do International Roadmap for Devices and Systems (IRDS), produzindo um guia quantitativo para pesquisadores e engenheiros do setor.

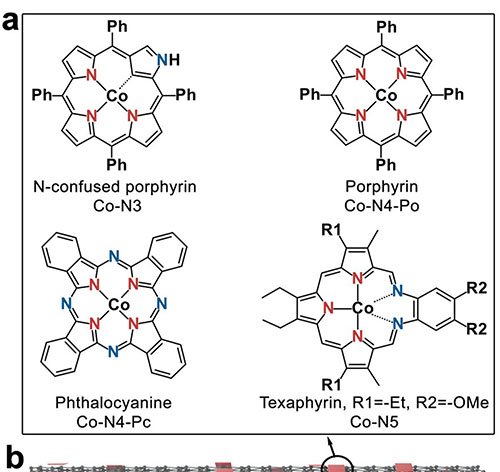

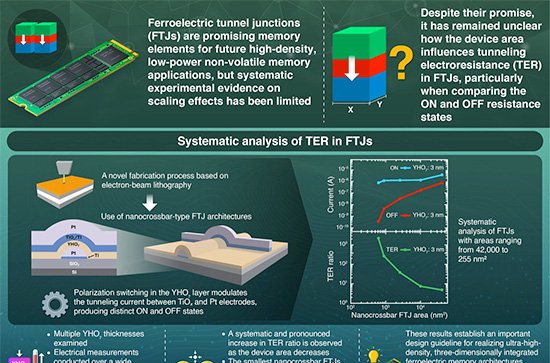

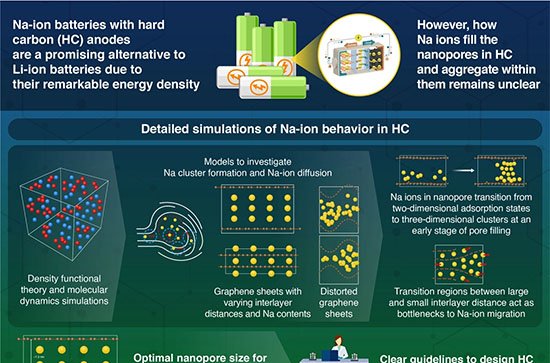

Materiais ferroelétricos e requisitos industriais

O trabalho também investigou o uso de materiais ferroelétricos no gate stack. Por manterem polarização elétrica sem alimentação externa, esses compostos prometem lógicas de ultrabaixo consumo, memória não volátil e computação em memória. O roteiro descreve exigências práticas, como processamento abaixo de 400 °C, uniformidade em escala de wafer e confiabilidade de longo prazo.

Imagem: Internet

“Este roteiro oferece um padrão para superar o maior desafio na comercialização de transistores 2D: obter gate stacks de alta qualidade”, afirmou o professor Lee. O grupo planeja ampliar a pesquisa em parceria com a indústria.

A orientação elaborada pela SNU fornece base para o desenvolvimento de chips de inteligência artificial, dispositivos móveis mais eficientes e servidores de alta densidade. O primeiro autor do artigo, o pesquisador de pós-doutorado Yeon Ho Kim, continuará focado na engenharia de contatos e gate stack para transistores 2D, contribuindo para a próxima onda de inovação em semicondutores.

Com informações de Nanowerk