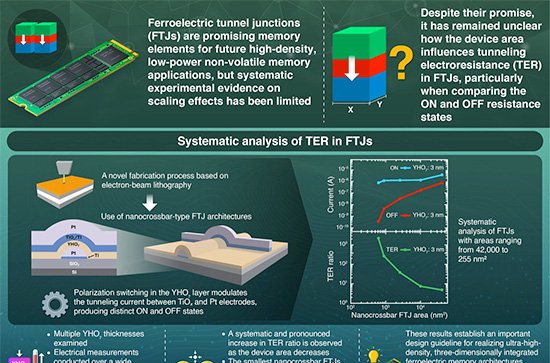

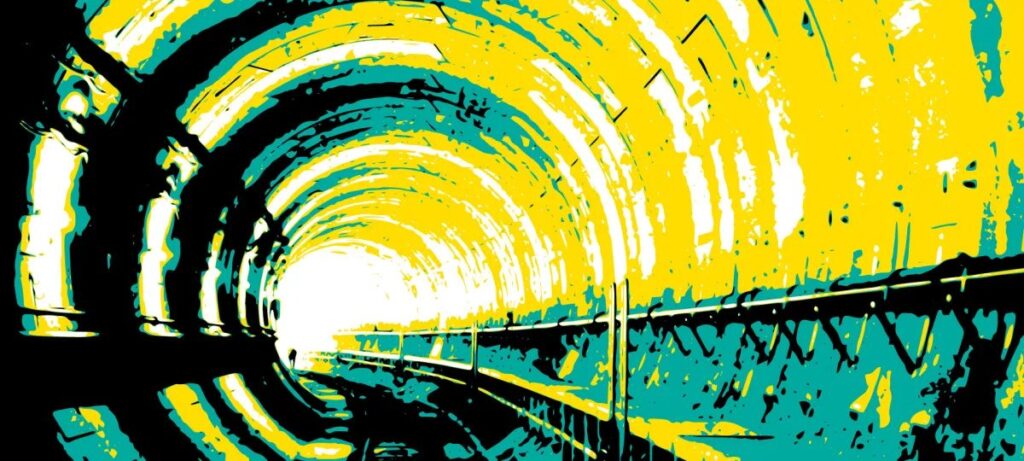

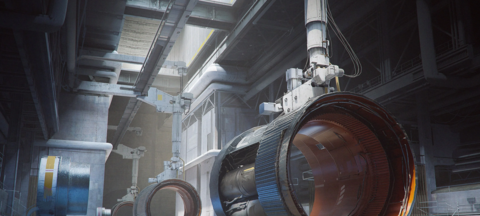

Pesquisadores do Institute of Science Tokyo demonstraram que reduzir o tamanho de junções túnel ferroelétricas (FTJs) construídas sobre silício pode aumentar drasticamente o contraste de resistência entre os estados ON e OFF, fator decisivo para a leitura de dados em memórias não voláteis.

O estudo, publicado em 23 de fevereiro de 2026 na revista Nanoscale, foi conduzido pela equipe do professor Yutaka Majima, do Materials and Structures Laboratory (MSL) do Institute of Innovative Research, em parceria com o professor Hiroshi Funakubo e o professor associado Seiichiro Izawa, todos da Science Tokyo.

Como foi feito

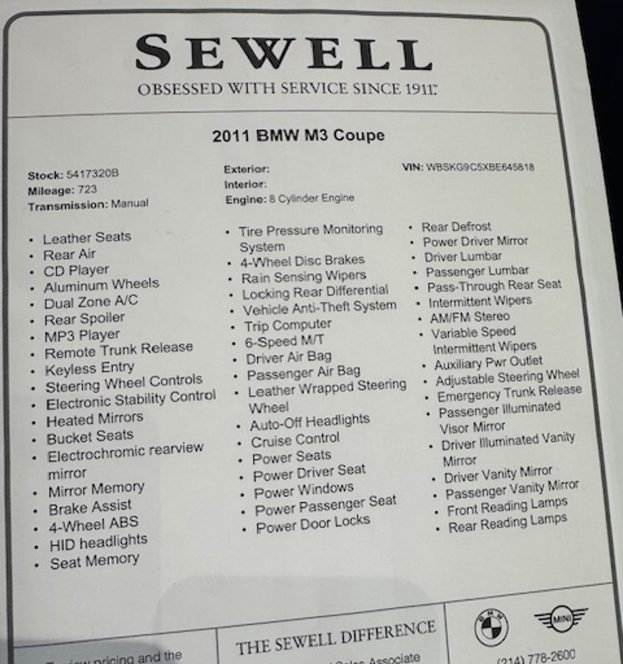

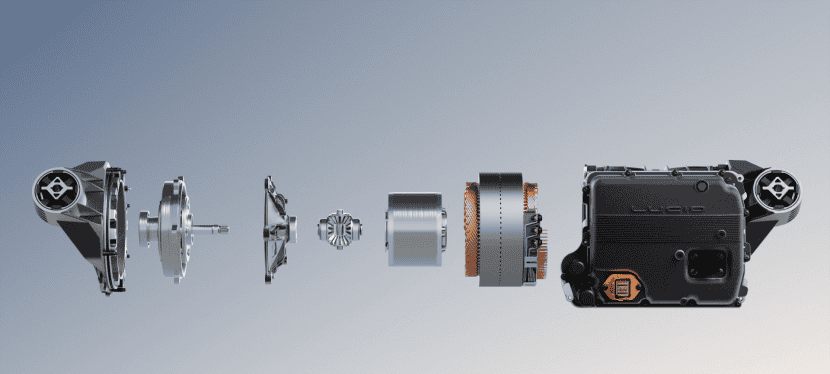

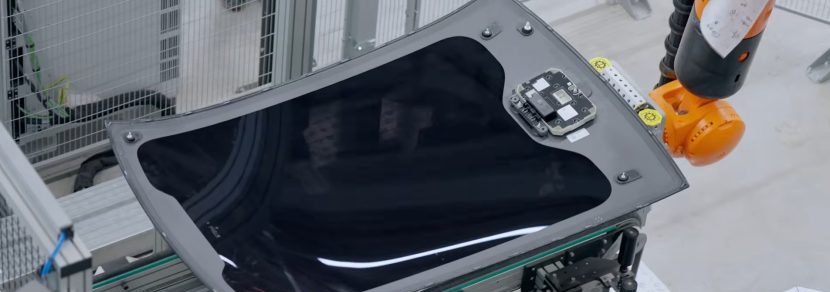

Os cientistas fabricaram FTJs com arquitetura de nanocrossbar diretamente em substratos de silício, usando litografia por feixe de elétrons. Cada dispositivo possui eletrodo superior de titânio/tióxido de titânio, barreira ferroelétrica de óxido de háfnio dopado com ítrio de 23 nm e eletrodo inferior de platina.

Resultados principais

As medições elétricas mostraram que os elétrons atravessam a barreira ferroelétrica por tunelamento quântico em ambos os estados, mesmo em temperaturas criogênicas. Ao encolher a área da junção, o índice TER – diferença relativa de resistência entre as polarizações – cresceu substancialmente. A menor estrutura, com largura de 25 nm, apresentou TER de 2.200, mais de dez vezes superior ao de dispositivos maiores.

Imagem: Internet

Relevância

Segundo Majima, o ganho de desempenho obtido com a miniaturização fornece diretrizes para memórias de alta densidade, baixo consumo e potencial integração tridimensional, demandas crescentes em aplicações de inteligência artificial, eletrônicos portáteis e Internet das Coisas.

Com informações de Nanowerk