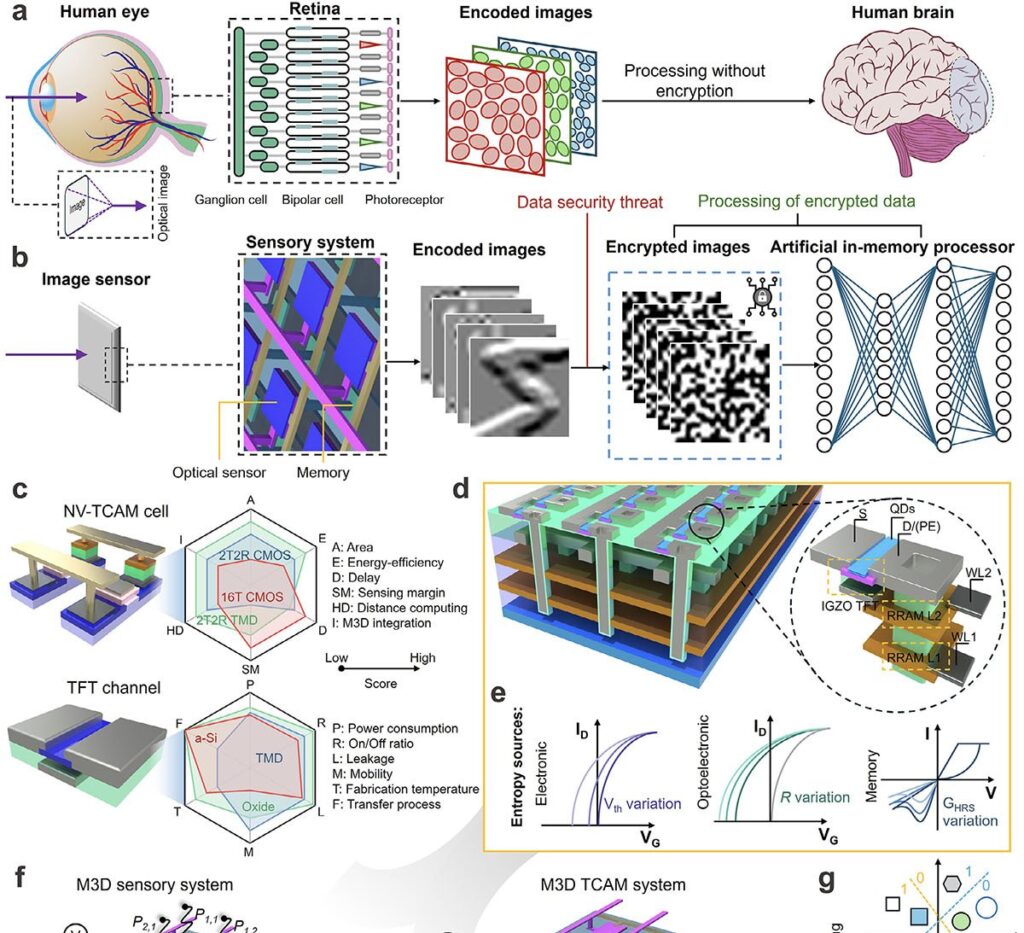

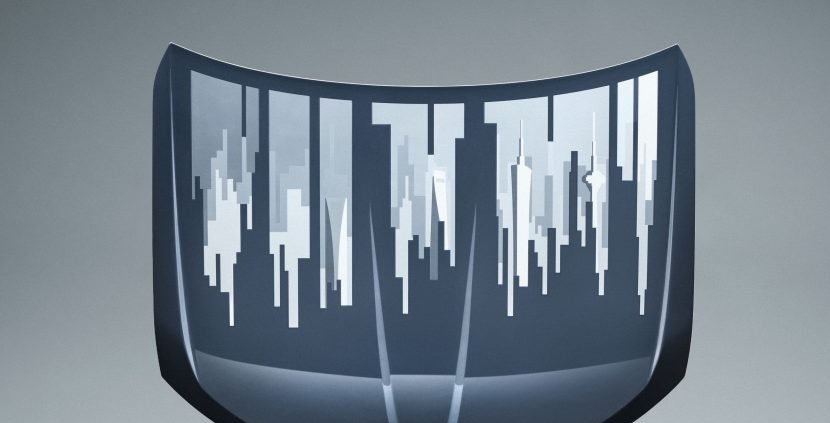

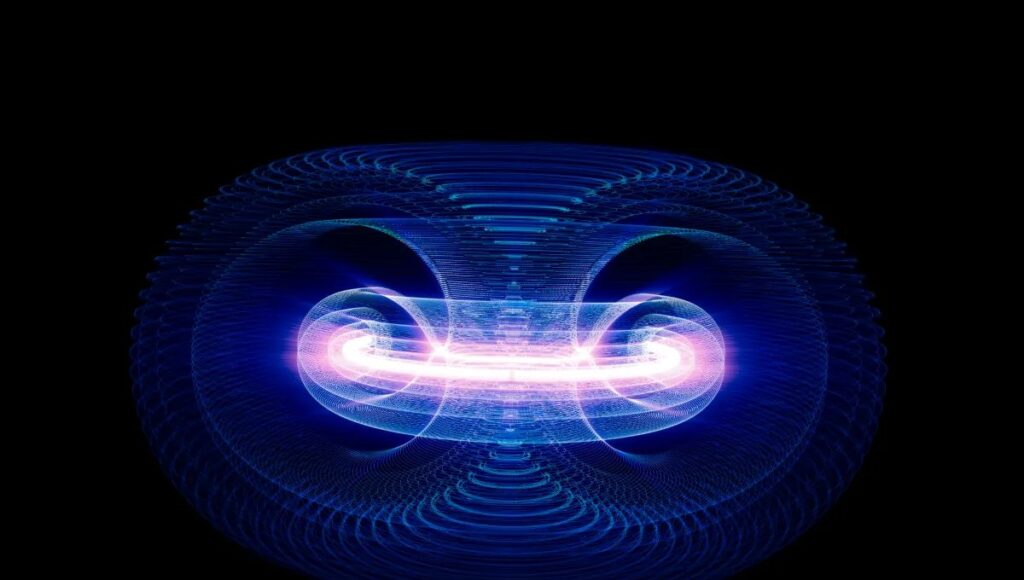

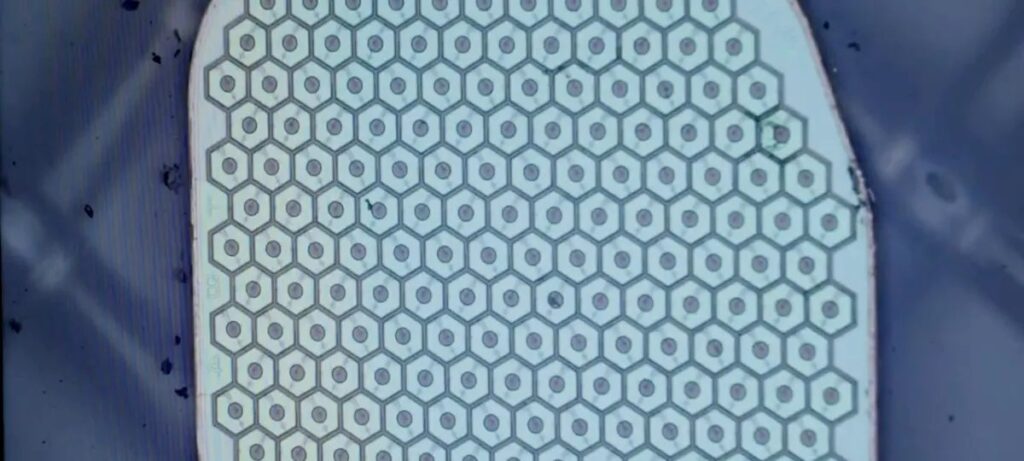

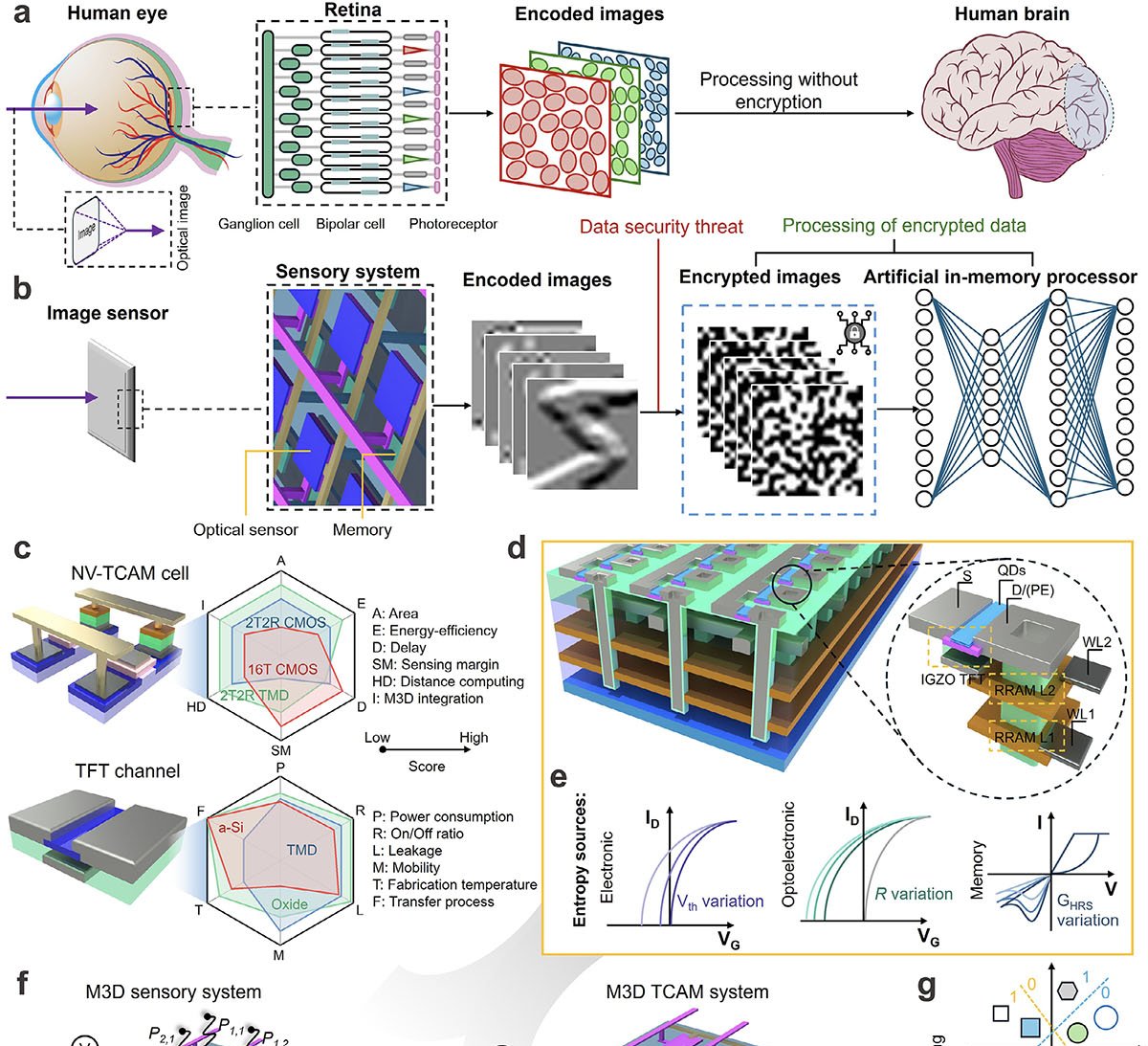

07 de novembro de 2025 – Um novo chip empilhado em três camadas reúne sensor de luz, memória resistiva e geração de chaves para capturar, armazenar e criptografar dados de imagem no próprio hardware, abrindo caminho para processamento seguro em tempo real em dispositivos de borda.

O dispositivo foi descrito por pesquisadores na revista Advanced Materials e combina duas camadas de memória resistiva vertical (VRRAM) com um fototransistor de filme fino de óxido de índio, gálio e zinco (IGZO) revestido por pontos quânticos de sulfeto de chumbo. Esse arranjo permite que o sinal óptico seja convertido diretamente em informação elétrica e gravado na memória sem circuitos intermediários.

Como funciona o empilhamento

• Duas camadas inferiores – VRRAM: armazenam os dados visuais e fornecem variabilidade elétrica natural, usada como fonte de aleatoriedade.

• Camada superior – fototransistor IGZO: sensível da luz ultravioleta ao infravermelho graças aos pontos quânticos, injeta carga na presença de luz e auxilia a programação das células de VRRAM.

As três camadas são fabricadas monoliticamente em um wafer de silício em baixa temperatura, evitando danos entre elas e resultando em um chip compacto.

Segurança incorporada

A variabilidade física de cada célula de VRRAM, a tensão de acionamento do fototransistor e a resposta óptica formam três fontes independentes de entropia. Esses parâmetros geram chaves de função fisicamente inclonável (PUF) com diferença média de cerca de 50% entre dispositivos, dificultando falsificação.

Após a captura, a informação é reduzida a códigos de hash por meio de locality sensitive hashing (LSH). Cada bit do hash é criptografado com a operação XOR usando a chave PUF. Esse método preserva a semelhança entre dados mesmo criptografados, permitindo buscas homomórficas — o chip compara entradas sem revelar o conteúdo original.

Imagem: Nanowerk https

Busca rápida em memória CAM

Para pesquisas em larga escala, o sistema integra memória associativa ternária (TCAM) formada pela pilha VRRAM-IGZO. A arquitetura vertical corta trilhas de fiação e reduz o número de transistores, alcançando mais de nove vezes a eficiência de área e mais de seis vezes a relação energia-velocidade em comparação a projetos bidimensionais convencionais.

Resultados experimentais

Em testes com imagens de dígitos manuscritos convertidas em hashes de 80 bits, a classificação por uma rede neural apresentou queda de apenas 0,2 ponto percentual quando os dados estavam criptografados. A busca por similaridade manteve mais de 94% do padrão observado em dados não criptografados.

Segundo os autores, a integração de detecção, memória e criptografia no mesmo stack reduz movimentação de dados e elimina a necessidade de módulos externos de segurança, favorecendo aplicações de Internet das Coisas que exigem resposta imediata e proteção de dados desde a origem.

Com informações de Nanowerk