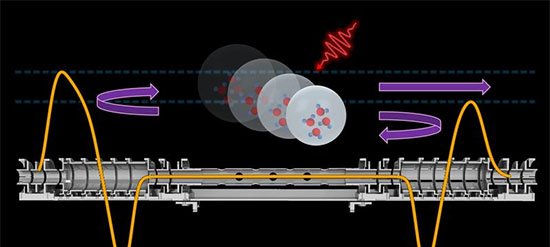

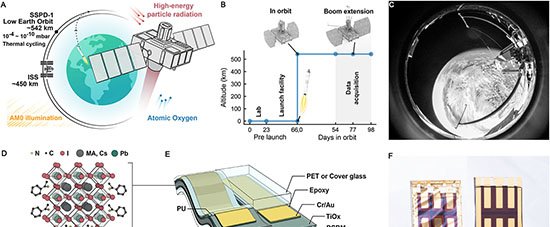

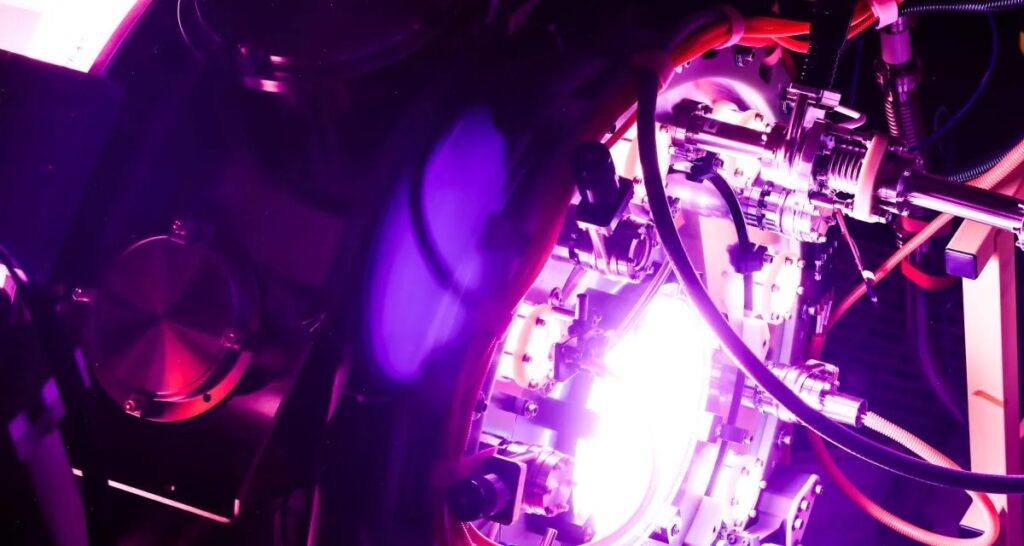

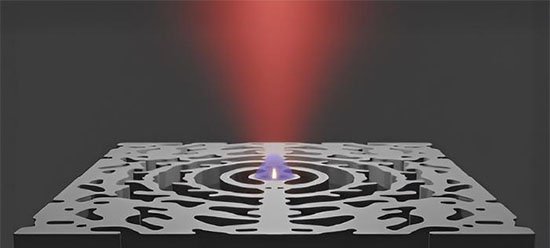

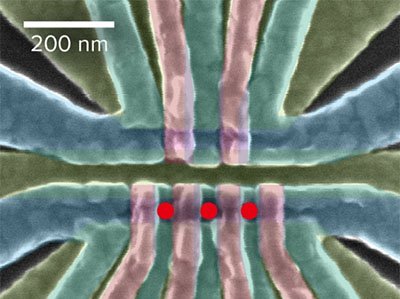

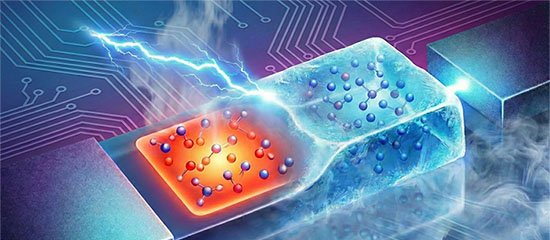

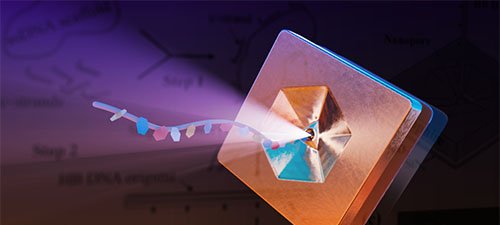

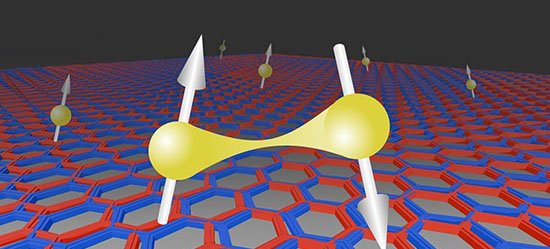

Pesquisadores da RWTH Aachen University e do Forschungszentrum Jülich, ambos na Alemanha, integraram memristores de dissulfeto de molibdênio (MoS₂) diretamente na fiação traseira de microchips CMOS de 350 nm, alcançando a menor tensão de chaveamento já registrada para um dispositivo de material bidimensional instalado em silício.

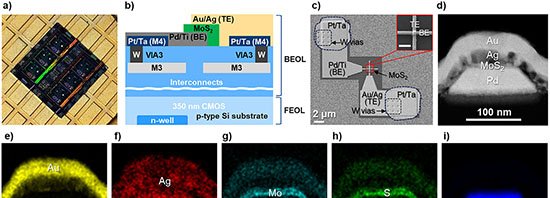

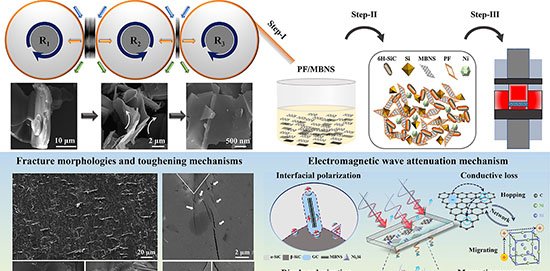

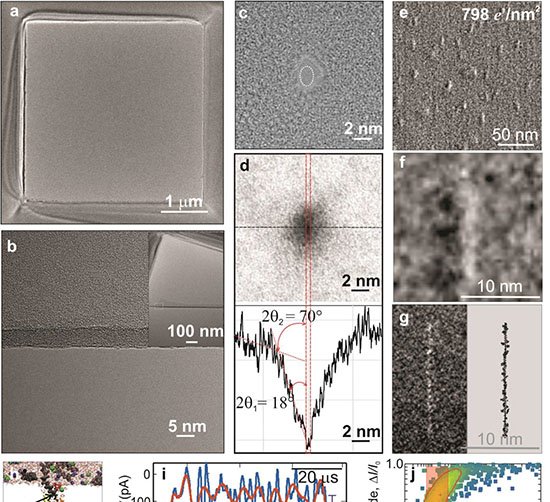

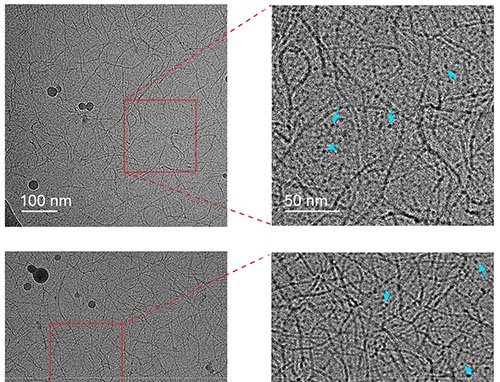

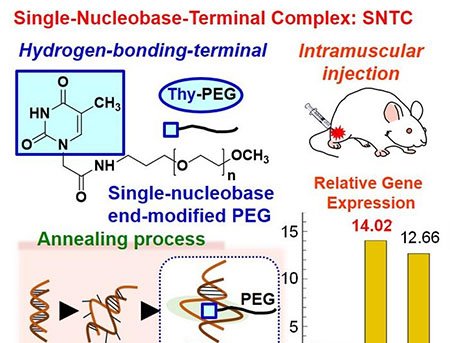

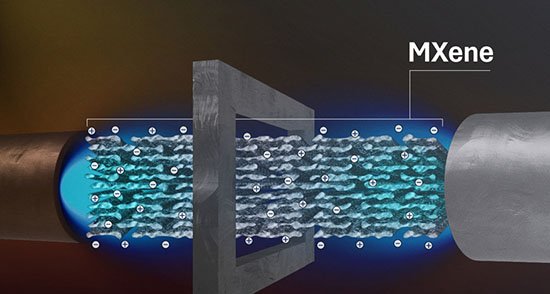

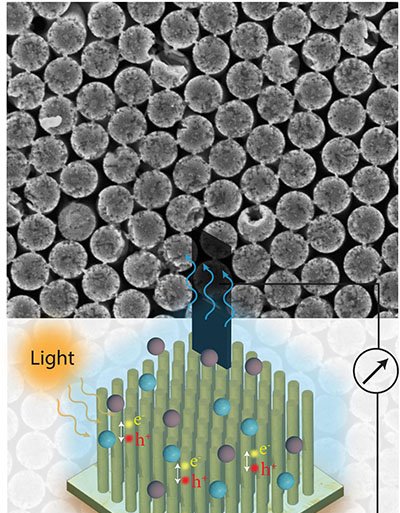

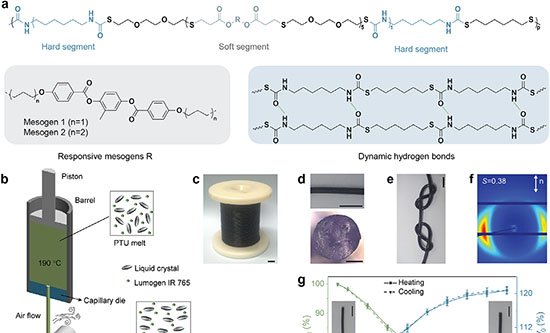

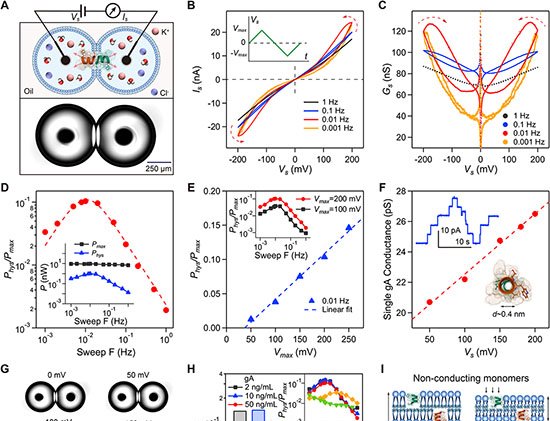

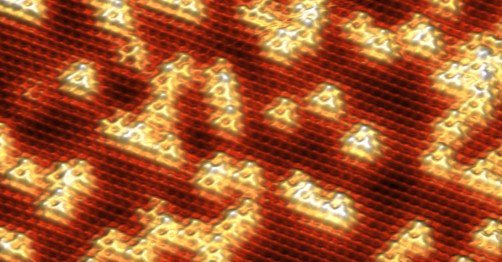

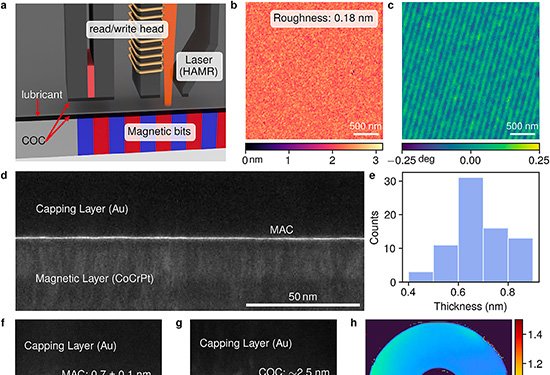

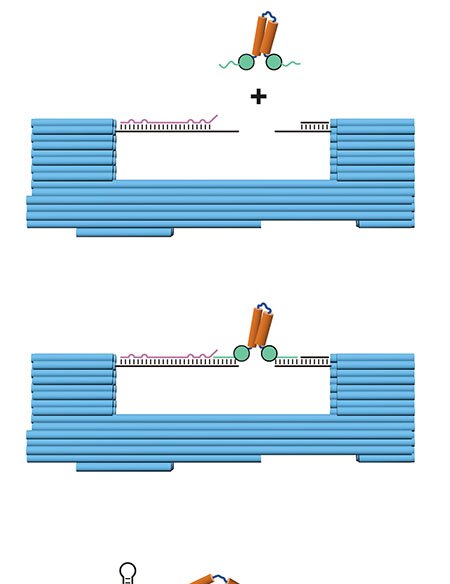

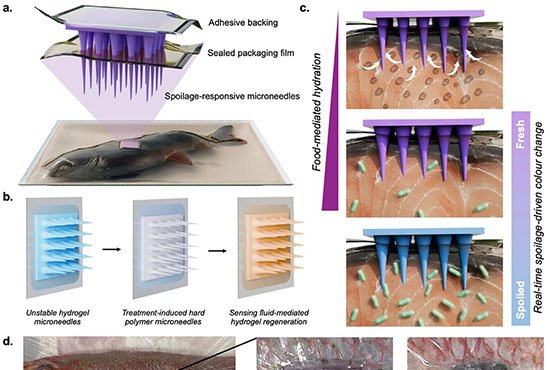

O estudo, publicado em 25 de fevereiro de 2026 na revista Advanced Functional Materials, descreve 19 células do tipo um-transistor-um-resistor (1T1R) formadas por eletrodos de ouro/prata e paládio separados por uma película de MoS₂ de 2,3 nm. Cada célula ocupa apenas 0,015 µm², o menor tamanho já relatado para memristores desse tipo.

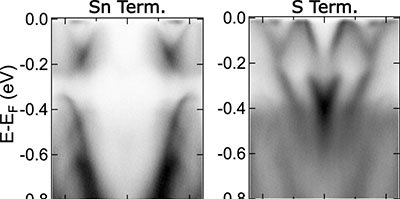

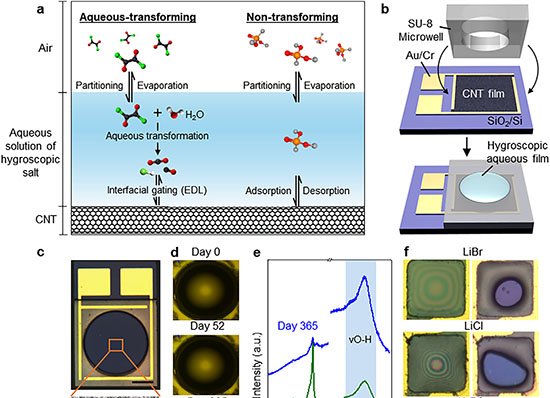

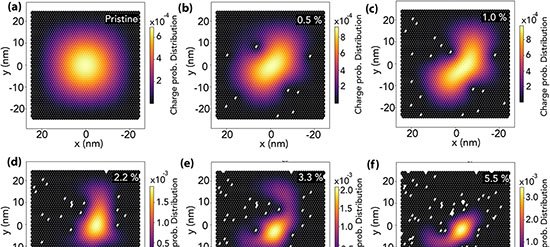

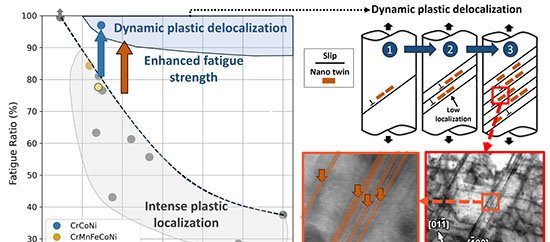

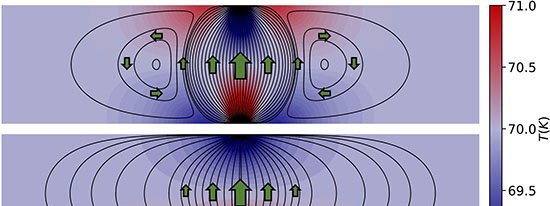

As memórias mudaram do estado de alta para baixa resistência com pulsos de aproximadamente 0,23 V para set e 0,1 V para reset, sem exigir a etapa inicial de “formatação” presente em outras tecnologias. Em um dispositivo, a variação ciclo a ciclo da tensão de set ficou abaixo de 10 % ao longo de 600 ciclos; outro componente superou 4 000 comutações sem degradação perceptível.

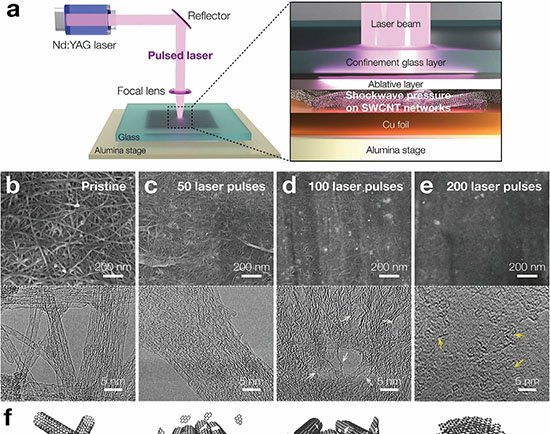

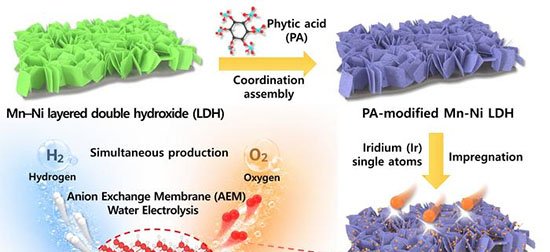

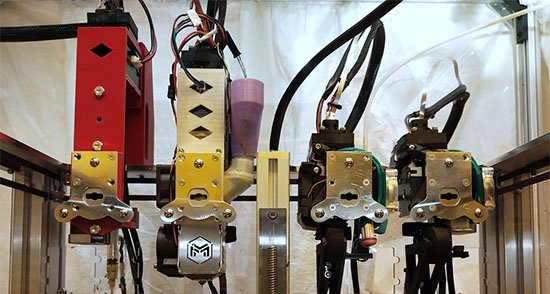

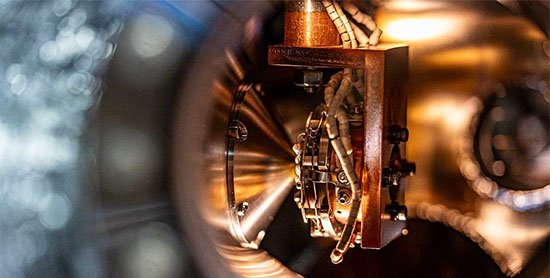

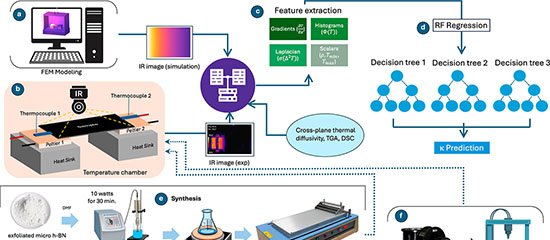

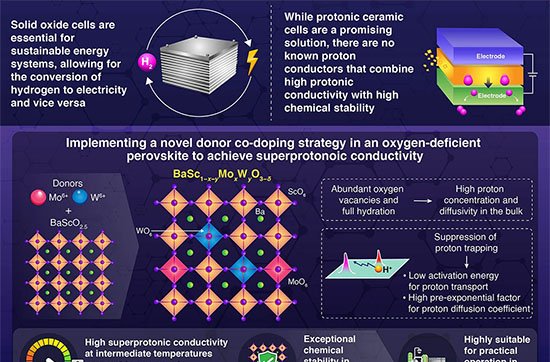

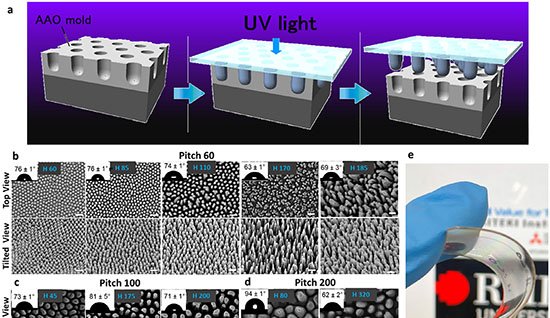

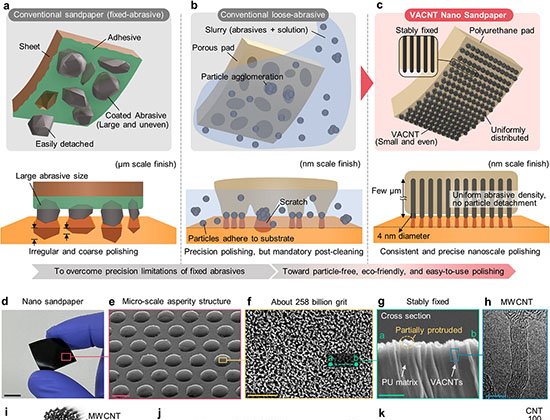

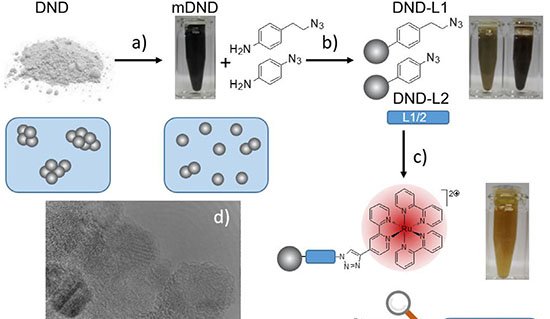

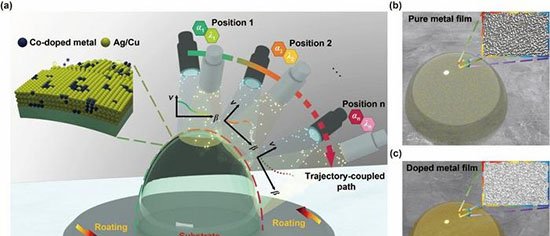

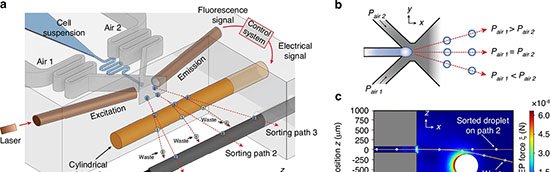

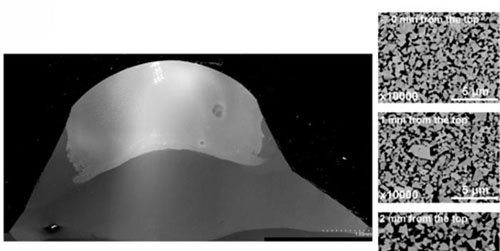

Para fabricar os componentes, a equipe manteve os pontos de contato de tungstênio dos chips expostos e adicionou uma quarta camada metálica de platina/tântalo que interliga os memristores aos transistores CMOS subjacentes. As películas de MoS₂, obtidas por deposição química de vapor metalorgânico em safira, foram transferidas para o silício antes da litografia eletrônica definir os eletrodos.

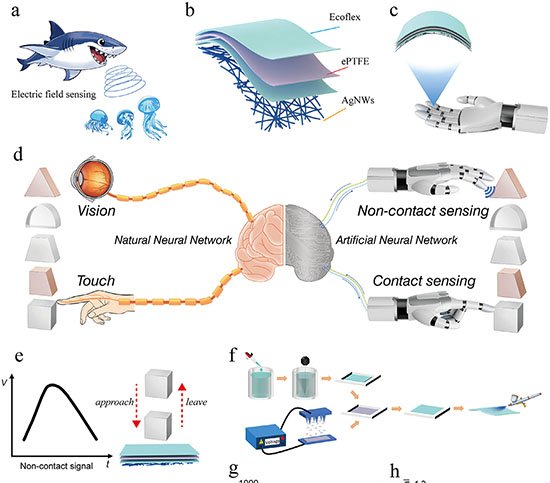

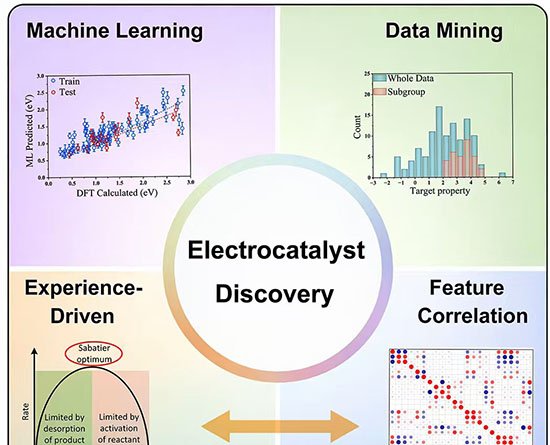

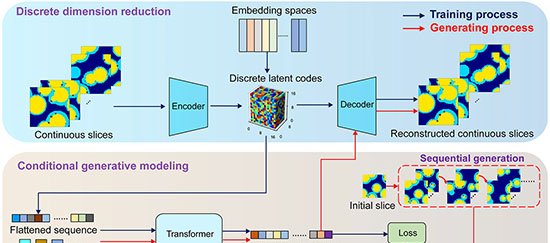

O transistor integrado limita com precisão a corrente durante a programação, reduzindo variações e confirmando a vantagem da integração total em CMOS. Ajustes na tensão de porta permitiram ainda a gravação de múltiplos níveis de resistência na mesma célula, recurso essencial para circuitos neuromórficos que dependem de pesos analógicos.

Imagem: Nanowerk https

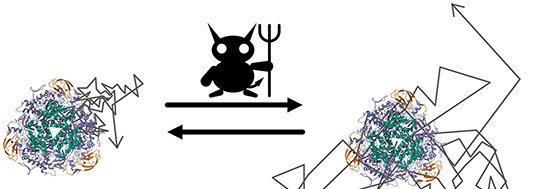

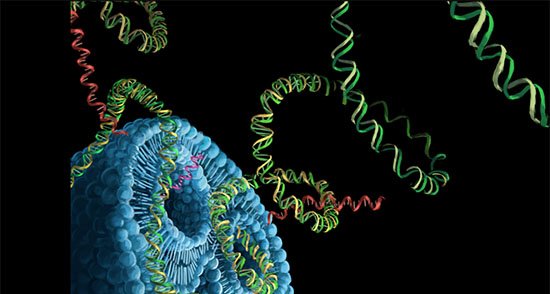

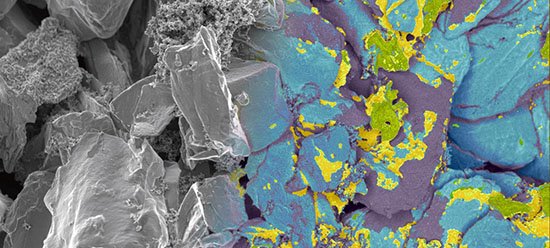

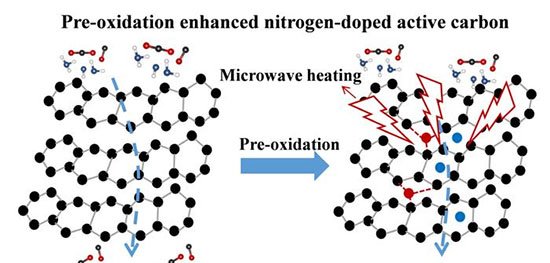

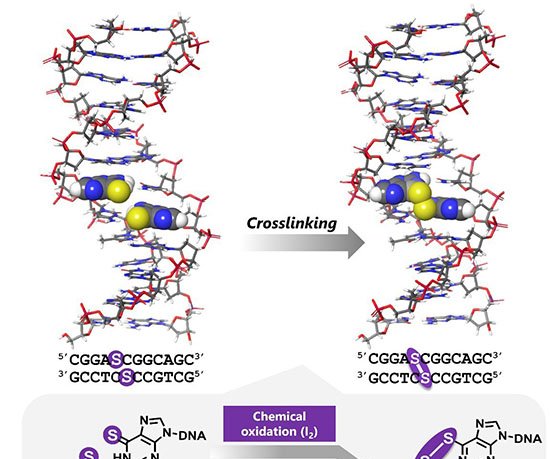

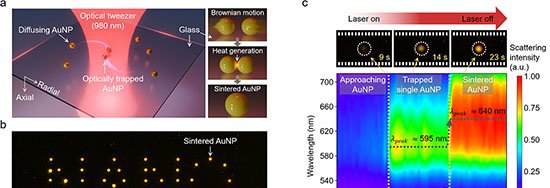

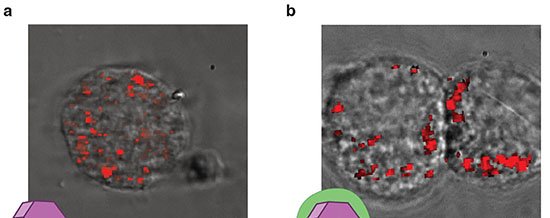

Análises por microscopia eletrônica revelaram que íons de prata migram pela camada de MoS₂ formando filamentos condutivos — mecanismo típico de metalização eletroquímica —, explicando a comutação entre estados.

Com área ultracompacta, operação sem passo de formação e tensões inferiores às de memristores baseados em h-BN já acoplados a CMOS, o dispositivo de MoS₂ avança a viabilização de memórias de baixa potência e arquiteturas de computação em memória dentro de processos industriais padrão.

Com informações de Nanowerk